ZYNQ | GPIO、MIO、EMIO

Intro

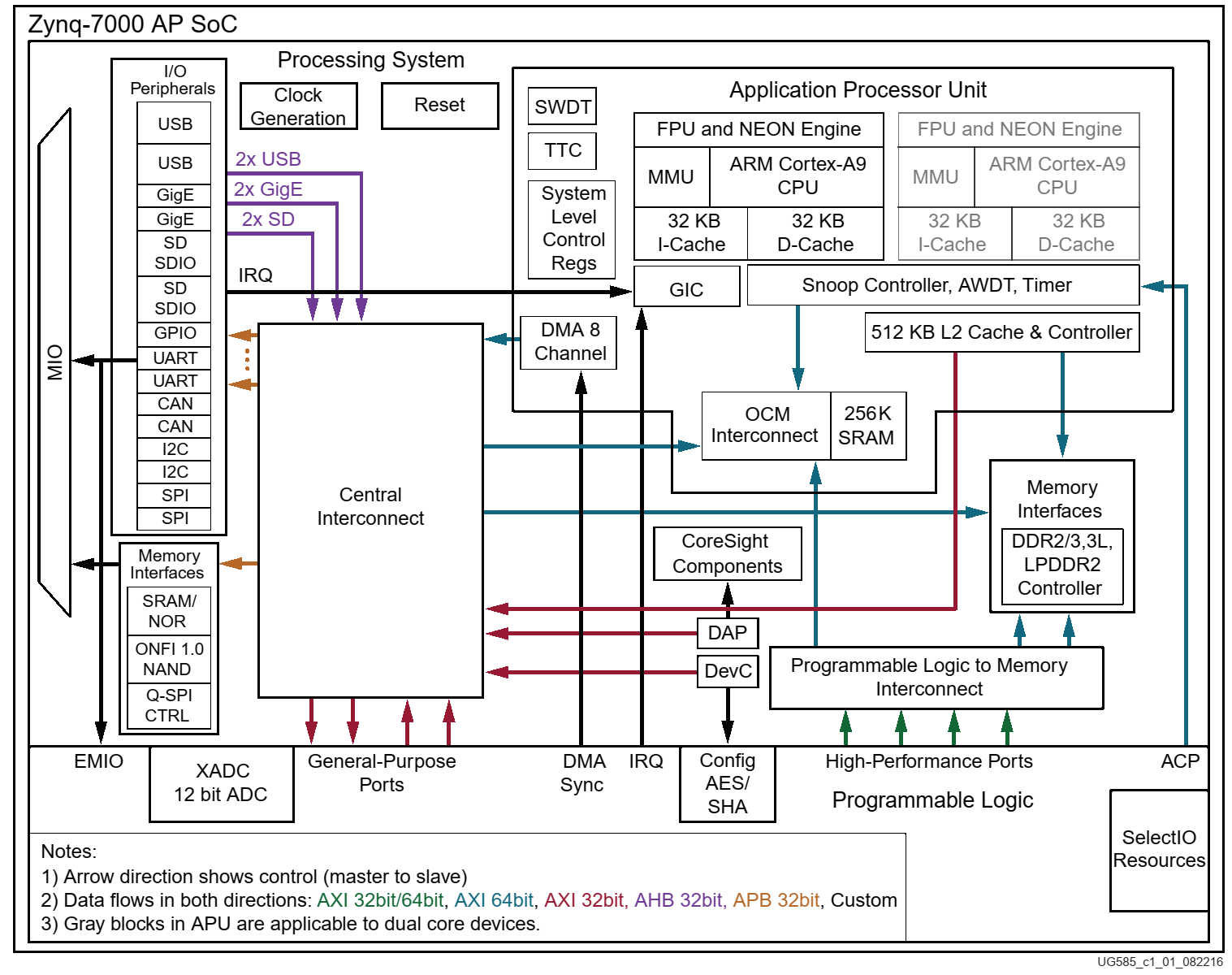

MIO与EMIO是ZYNQ芯片PS部分一个相当重要的接口。GPIO是MIO的一部分,要了解GPIO,首先需要了解ZYNQ的整体架构。

ZYNQ主要由以下主要功能区块组成,这些模块均能在上图中找到对应的位置:

- Processing System(PS)

- Application processor unit(APU)

- Memory interface

- I/O peripherals(IOP)

- Interconnect

- Programmable Logic(PL)

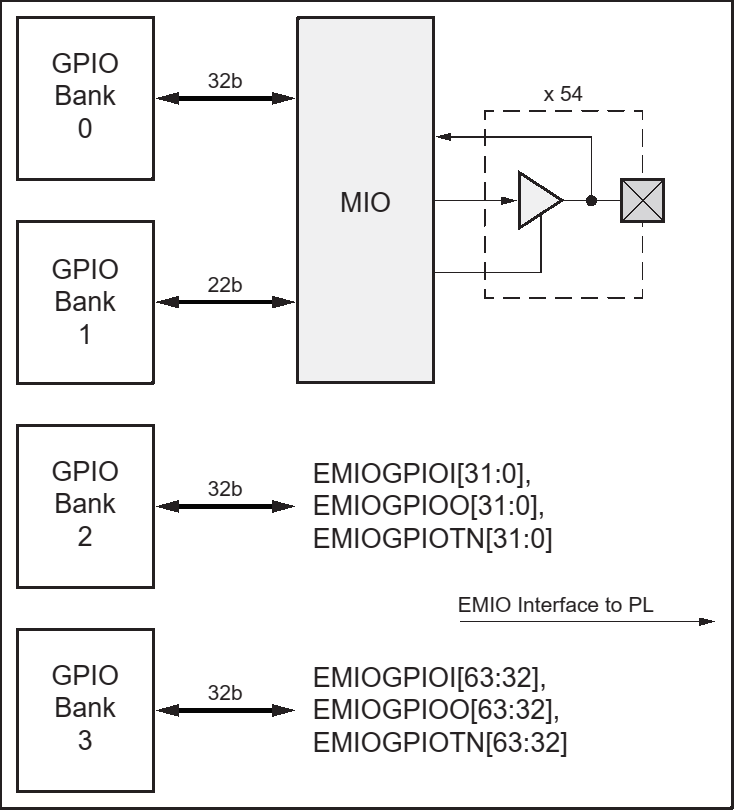

GPIO处于IOP中,是一个外设,能通过MIO模块能对器件的引脚进行操作,同时也通过EMIO提供了对PL的访问能力(包括64个inputs和128个outputs)。

The general purpose I/O (GPIO) peripheral provides software with observation and control of up to 54 device pins via the MIO module. It also provides access to 64 inputs from the Programmable Logic (PL) and 128 outputs to the PL through the EMIO interface. The GPIO is organized into four banks of registers that group related interface signals.

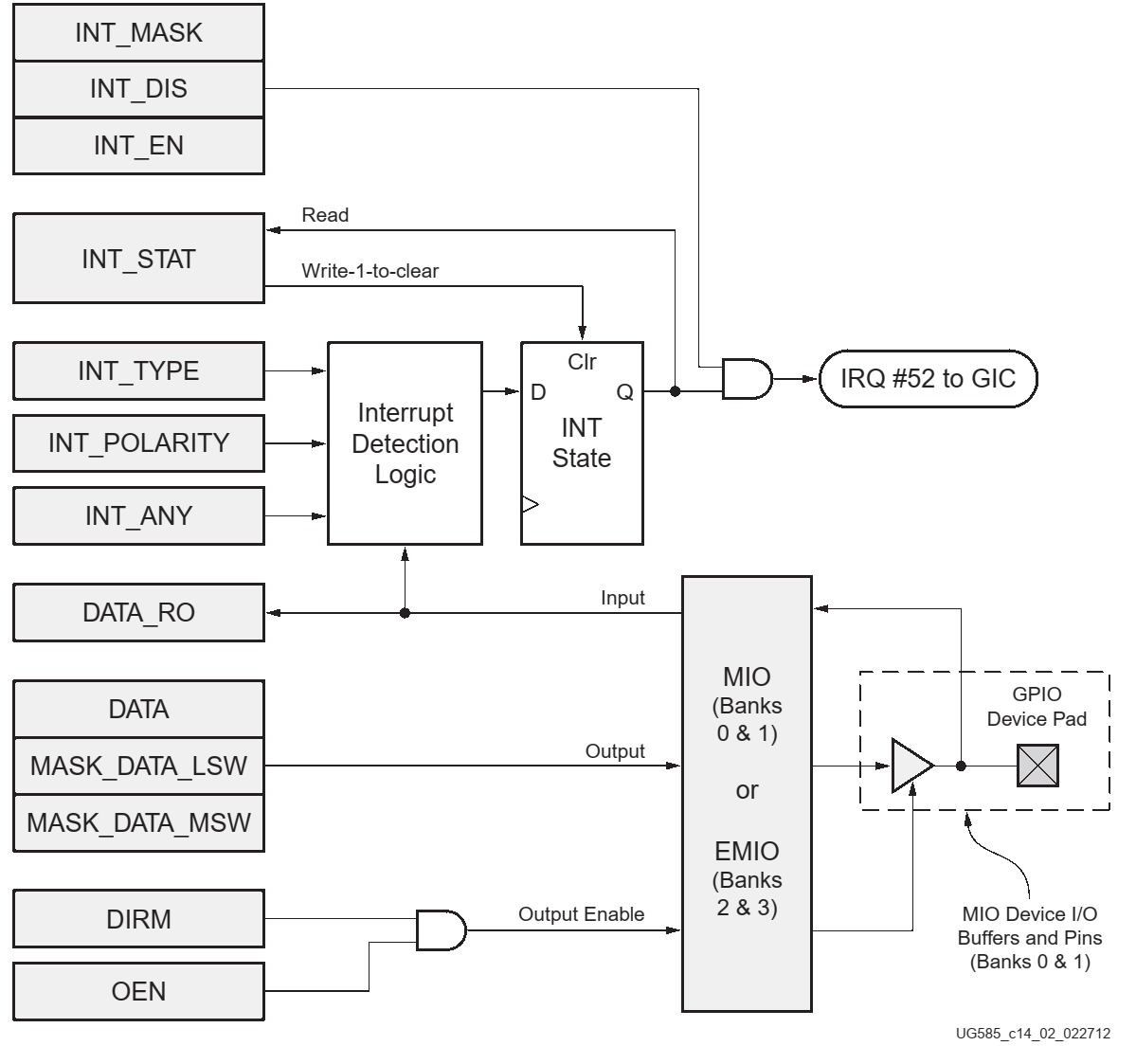

Each GPIO is independently and dynamically programmed as input, output, or interrupt sensing. Software can read all GPIO values within a bank using a single load instruction, or write data to one or more GPIOs (within a range of GPIOs) using a single store instruction. The GPIO control and status registers are memory mapped at base address 0xE000_A000.

对GPIO的控制是通过一系列存储器映射(Memory Mapped)的寄存器实现的。

可以看到这里的MIO/EMIO与寄存器的连接方式都是一样的,