FPGA时钟无毛刺切换电路

时钟无毛刺切换电路

(文字由AI润色完成)

本文旨在对几种经典的时钟切换电路进行梳理和总结。

具体的时钟切换时序图可以参考网上各大博客。

有毛刺的切换电路

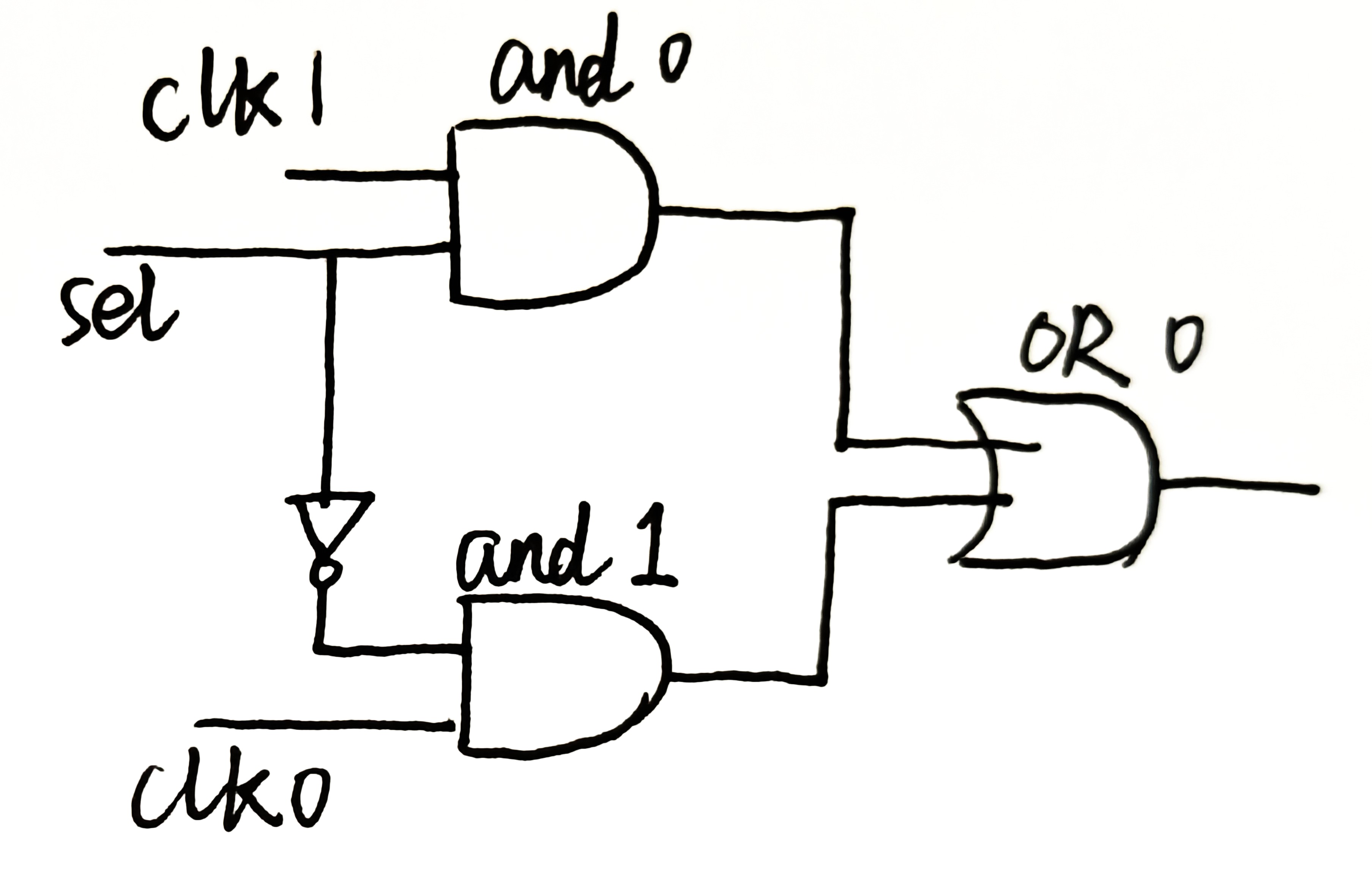

下图是一个由基本门电路构成的时钟选择器。其本质就是一个组合逻辑的多路选择器(MUX)。

问题所在:选择信号 sel 相对于 clk0 和 clk1 都是异步的。如果 sel 的跳变发生在任一时钟的高电平期间,输出端 clk_out 就可能产生一个非常窄的脉冲,即“毛刺”。这个毛刺会被下游逻辑误采,引发功能错误。

无毛刺时钟切换电路

为了规避上面的异步信号带来的影响,需要加入同步电路,即打2拍把异步信号同步到本地时钟域。

实现无毛刺切换的核心原则是 “先停后启”:即先关闭当前输出的时钟,再开启新的时钟,确保切换过程中不会产生不完整的时钟脉冲。

相关时钟

当两个时钟源 clk0 和 clk1 存在明确的频率或相位关系(如倍频、分频)时,可以采用如下相对简单的设计。

这里本质上sel信号相对于clk0和clk1仍然是异步信号,但由于这里时钟存在相关性,对异步sel信号进行一定的约束即可规避掉亚稳态问题。

非相关时钟

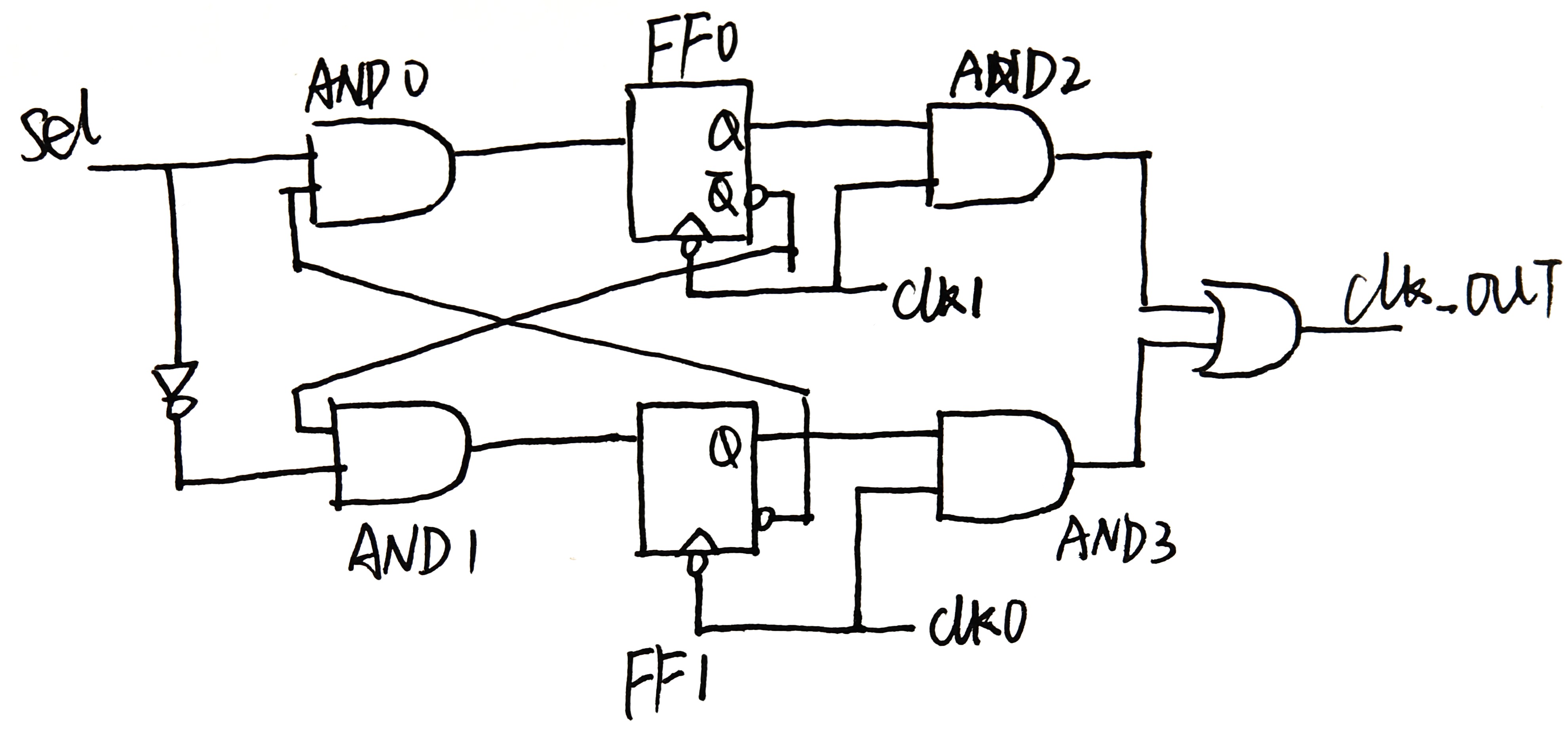

这是最通用、最稳健的设计,适用于两个时钟之间无任何关联的场景。

该电路的逻辑非常精妙。下面以 sel 从 0 切换到 1 (即时钟从 clk0 切换为 clk1)为例说明:

- 关闭 clk0:

sel变为1后,该信号被clk0域的两级触发器(FF2, FF3)同步。由于 FF3 是下降沿触发,它会在clk0的下降沿(即低电平)到来后,才改变其输出。FF3/Qn变为0,从而安全地关闭通往clk0的与门(AND3)。注意此时时钟输出为低电平。 - 开启 clk1:

FF3/Qn输出的0会传递给clk1域的两级触发器(FF0, FF1)。同样,由于 FF1 是下降沿触发,它会在clk1的下降沿到来后,才使其输出FF1/Q变为1,从而安全地打开通往clk1的与门(AND2)。

至此,时钟源被平稳地从 clk0 切换到了 clk1,全程无毛刺风险。

简单总结流程是:sel信号从0到1,经历2级clk0同步关闭clk0,经历2级clk1同步打开clk1。

RTL code

代码编写还是比较容易,将电路描述出来即可。为了仿真观察波形,笔者加入了0.1个时间单位的延迟。

1 | |

总结

- 用纯组合逻辑(MUX)进行异步时钟切换,极易产生毛刺。

- 设计中的下降沿触发是关键,它确保了对时钟路径的使能/禁止操作都发生在时钟的稳定低电平期间。

参考

- CSDN|Glitch free 无毛刺时钟切换电路、时钟无缝切换、时钟无毛刺切换技术

- 博客园|时钟切换电路(无毛刺)——clock switching glitch free

- 知乎专栏|时钟无毛刺切换电路(glitch free)

FPGA时钟无毛刺切换电路

https://blog.zorogh.top/2025/08/25/glitch-free-clock-switching/